- Information

- AI Chat

This is a Premium Document. Some documents on Studocu are Premium. Upgrade to Premium to unlock it.

Was this document helpful?

This is a Premium Document. Some documents on Studocu are Premium. Upgrade to Premium to unlock it.

VLSI Design Module - 3 - Vtu notes of ece 7th sem vlsi 3rd mod 18th scheme

Course: Electronic and communication (ECE)

999+ Documents

Students shared 1755 documents in this course

University: Visvesvaraya Technological University

Was this document helpful?

This is a preview

Do you want full access? Go Premium and unlock all 25 pages

Access to all documents

Get Unlimited Downloads

Improve your grades

Already Premium?

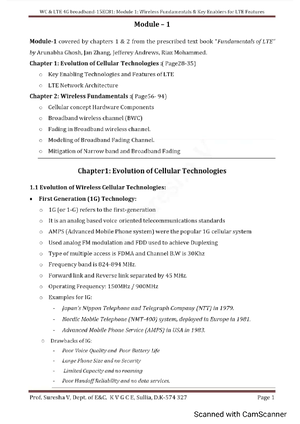

VLSI Design

Page 1

Module - 3

Syllabus:

Delay: Introduction, Transient Response, RC Delay Model, Linear Delay Model, Logical

Efforts of Paths (4.1 to 4.5 of TEXT2, except sub-sections 4.3.7, 4.4.5, 4.4.6, 4.5.5 and 4.5.6).

Combinational Circuit Design: Introduction, Circuit families (9.1 to 9.2 of TEXT2, except

subsection 9.2.4).

Textbooks:

1. “CMOS Digital Integrated Circuits: Analysis and Design” - Sung Mo Kang & Yosuf

Leblebici, Third Edition, Tata McGraw-Hill.

2. “CMOS VLSI Design- A Circuits and Systems Perspective”- Neil H. E. Weste and

David Money Harris, 4th Edition, Pearson Education.

Delay

Definitions:

Propagation delay time, tpd:

Maximum time from the input crossing 50% to the output crossing 50%

Contamination delay time, tcd:

Minimum time from the input crossing 50% to the output crossing 50%

Rise time, tr:

Time for a waveform to rise from 20% to 80% of its steady-state value

Fall time, tf:

Time for a waveform to fall from 80% to 20% of its steady-state value

Edge rate,

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.

Why is this page out of focus?

This is a Premium document. Become Premium to read the whole document.